Exercice Electronique Théorème Thévenin

Exercice (électronique) :

On considère le circuit de la figure 1 avec R = RL = 1 K? et E = 20V.

- On demande de trouver le générateur de Thévenin (VTH et RTH) équivalent vu entre les points N et M pour les cas ou a) R0 = 0 et b) R0 est infinie. Que peut-on en déduire ?

- Exercice_Electronique_L1-S1

Correction de l’examen FE2

Correction de l’examen FE2_geii- L2

1°) Table de vérité

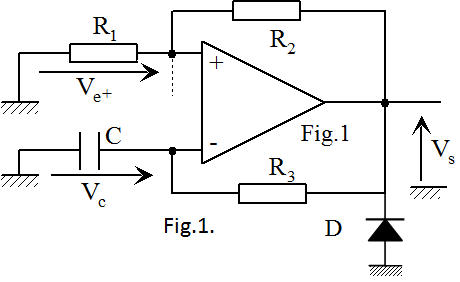

2°) On suppose au départ que Vs = +VCC. Etude du fonctionnement du circuit en traçant les évolutions des tensions aux points, A, B, D, F, VS et aux bornes de la capacité C (Vc). Le seuil de basculement des portes est pris égal à (VCC/3).

Correction de l’examen « Logique combinatoire » & Consultation des copies

Correction de l’examen du module « Logique combinatoire – Mai 2016 – L1 – S2 – ENST

Note: La consultation des copies se fera le dimanche 5 juin de 10h à 12h00.

Exercices de révision L2_GEII

Des exercices avec solutions sont proposés aux étudiants de l’ENST.

Cela concerne des révisions pour les L2 « Fonctions de l’électronique 2

Exercices logique combinatoire

Exercices logique combinatoire pour les étudiants de l’ENST.

Exercices oscillateurs

Exercice 1:

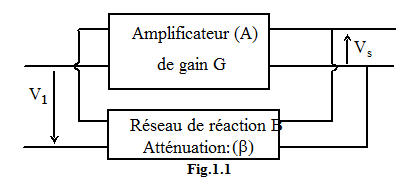

Soit un amplificateur A de gain G et de résistance d’entrée Re; Re . Cet amplificateur est associé à une boucle de réaction, formée par un quadripôle passif B qui introduit une atténuation (figure 1.1).

Fig.1.1

1°) Exprimer le rapport (Vs/V1).

2°) A quelle condition la tension Vs peut-elle garder une valeur finie lorsque V1 0? Que peut-on dire de ce système lorsque la condition précédente est vérifiée.

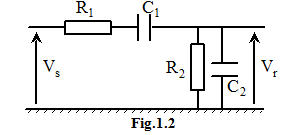

On considère le quadripôle passif de la figure 1.2. 0n demande:

Fig.1.2

Fig.1.2

3°) Calculer la fonction de transfert de ce circuit. Ce quadripôle prend l’emplacement du circuit passif désigné par B dans la figure 1.1 pour réaliser un oscillateur. Donner le schéma de cet oscillateur.

Solution

Correction_exercice_logique combinatoire_L1_S2

Codeur de priorité Octal-Binaire

Solution :

- Table de vérité

| Entrées (octal) | Sorties | |||||||||

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | S2 | S1 | S0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | x | x | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | x | x | x | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | x | x | x | x | 1 | 0 | 0 |

| 0 | 0 | 1 | x | x | x | x | x | 1 | 0 | 1 |

| 0 | 1 | x | x | x | x | x | x | 1 | 1 | 0 |

| 1 | x | x | x | x | x | x | x | 1 | 1 | 1 |

- Expressions logiques des sorties en fonction des entrées

S0 = A1 + A3 + A5 + A7

S1 = A1 + A3 + A5 + A7

S2 = A4 + A5 + A6 + A7

Exercices d’application_L2

Exercices d’application_L2